# Отдел Радиоэлектроники 2005/ 2006 Отчёт и Планы

Головцов В.Л. Гатчина, Декабрь 2005

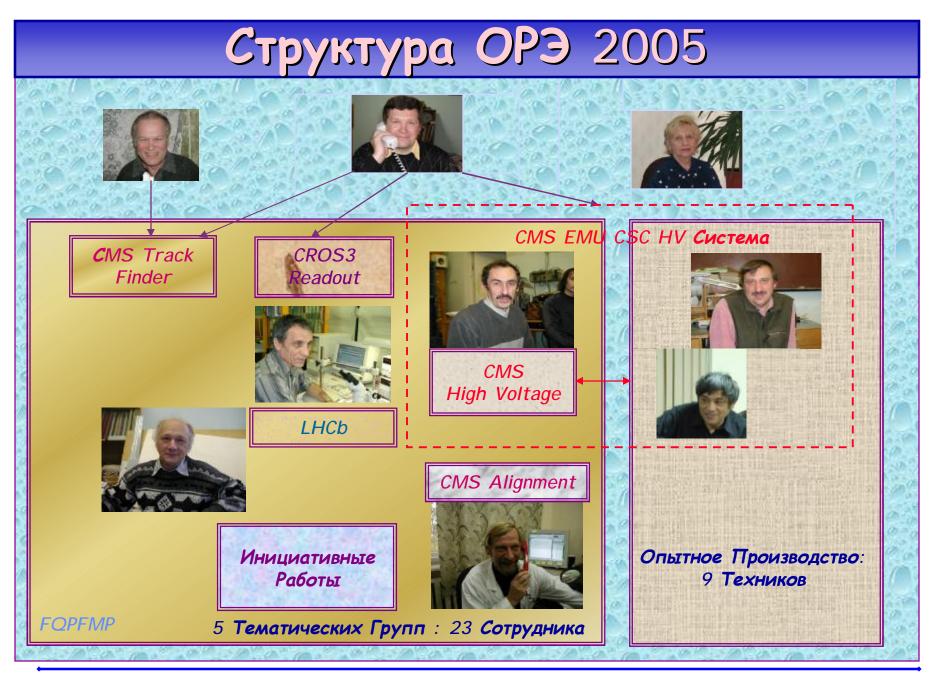

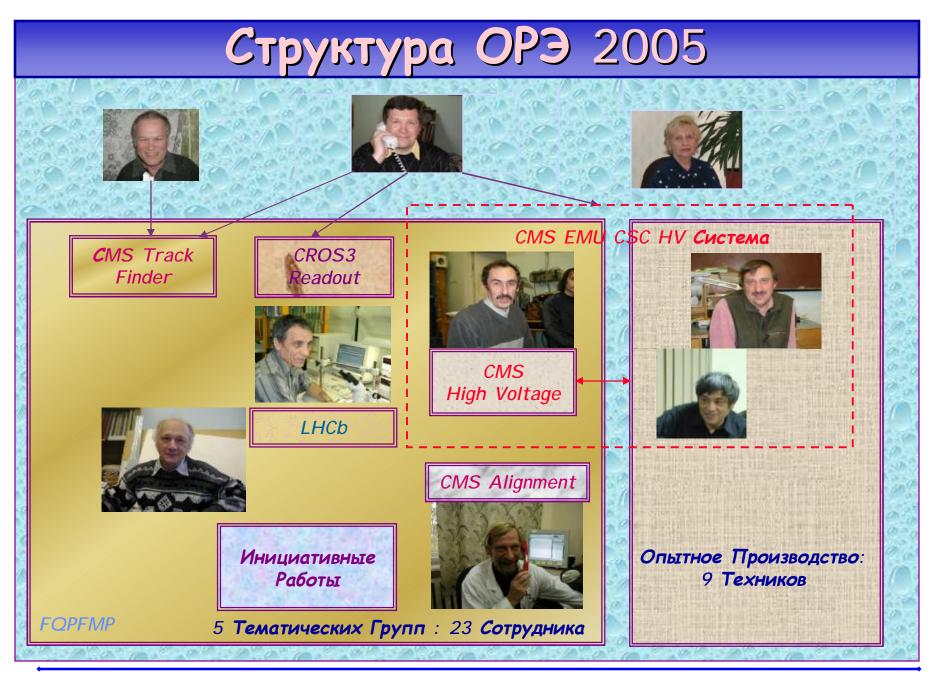

# OP3 2005

| Всего Сотрудников   | 30 |

|---------------------|----|

| Научных Сотрудников | 9  |

| Инженеров           | 12 |

| Техников            | 9  |

| Женщин              | 11 |

| Мужчин              | 19 |

| Пенсионеров         | 19 |

| В возрасте до 40    | 5  |

| Средний возраст     | 50 |

| Уволилось в 2005    | 2  |

### Основные Тематические Группы 2005

### Track Finder (CMS):

Головцов В.Л., Уваров Л.Н.

**FOPFMP**

#### CROS3:

Головцов В.Л., Бондарь Н.Ф., Яцюра В.И., Голяш А.Г., Лобачёв Е.А.

#### CMS EMU HV (CMS)

Волков С.С., Лазарев В.И., Исаев Н.Б., Бондарев С.В., Сергеев Л.О. Мыльникова А.В., Гулина Н.М.

### Alignment (CMS):

Скнарь В. А.

### **CMS Track Finder**

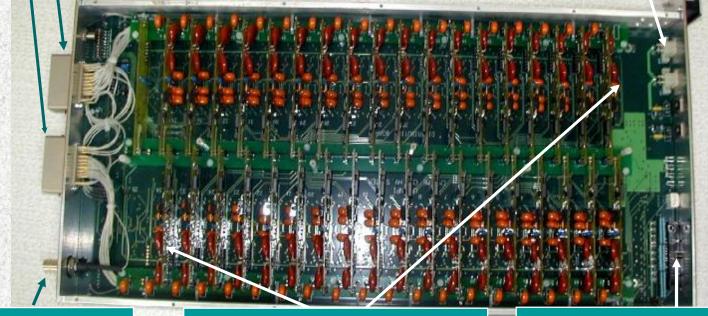

Серийные модули Процесора (SP05)

Track Finder разработан для мюонной триггерной системы CMS.

Реализуется как 12 Процессоров, каждый из которых идентифицирует до 3 лучших мюонных треков в 60-градусном азимутальном секторе. Анализирует входные примитивные треки (сегменты) от индивидуальных камер, восстанавливает полные треки по четырём камерам, измеряет поперечный импульс Pt

Ноябрь 1998 - подписание MOU с UF. 1999 - начало проектирования

2000-2001- выпуск первогоПрототипа, отладка и тестирование

В 2001 г. предложено новое идеологическое решение, позволившее реализовать второй прототип Процессора на одной сверхбольшой микросхеме FPGA.

В результате время решения Процессора сократилось с 375 ns до 175 ns, а число плат Track Finder - с 48 до 12 (один 9U-крейт VME)

2002-2003 - выпуск Прототипа SP02, отладка и тестирование

2004 - выпуск Прототипа SP04, отладка и тестирование

2005 - выпуск сигнального образца и массовое производство SP05

FOPFMP

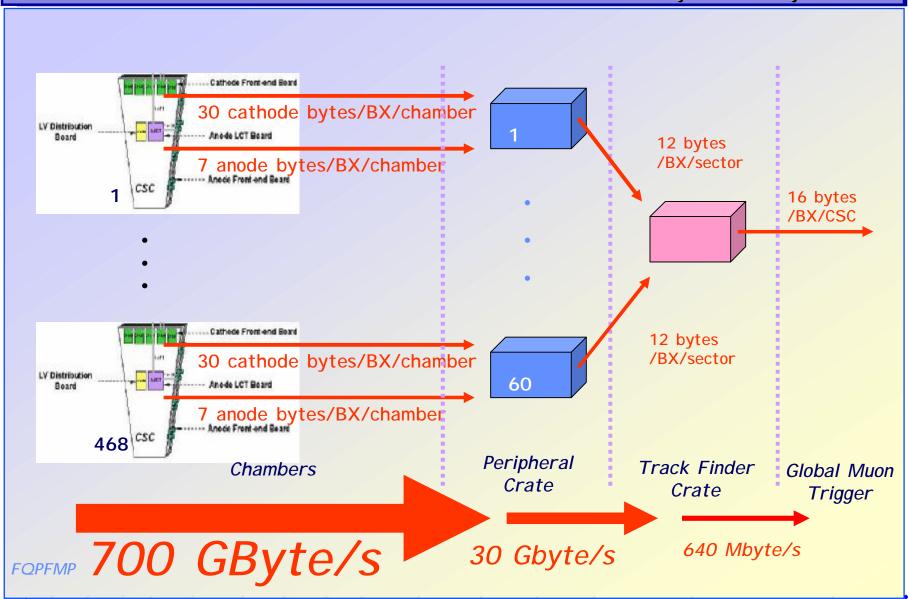

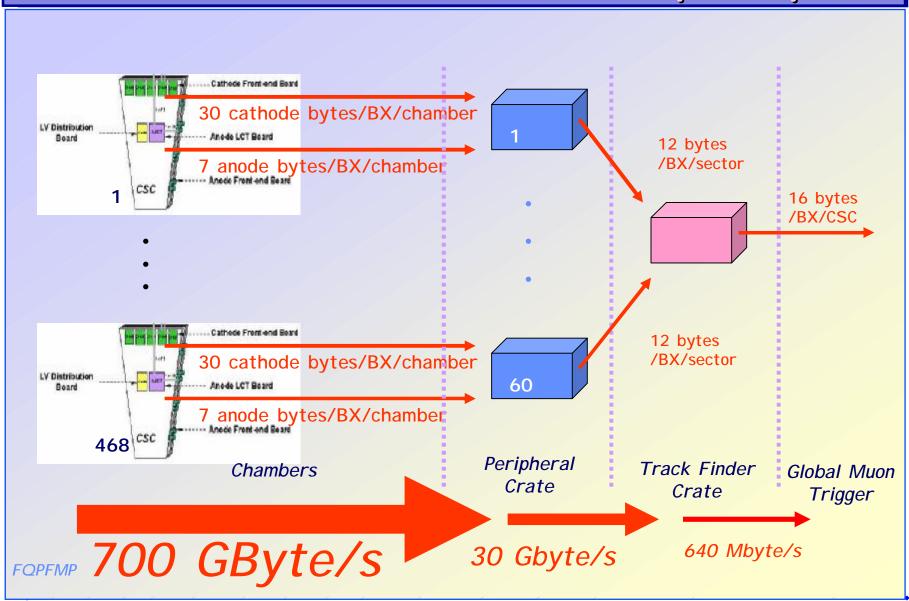

## Потоки данных мюонного триггера

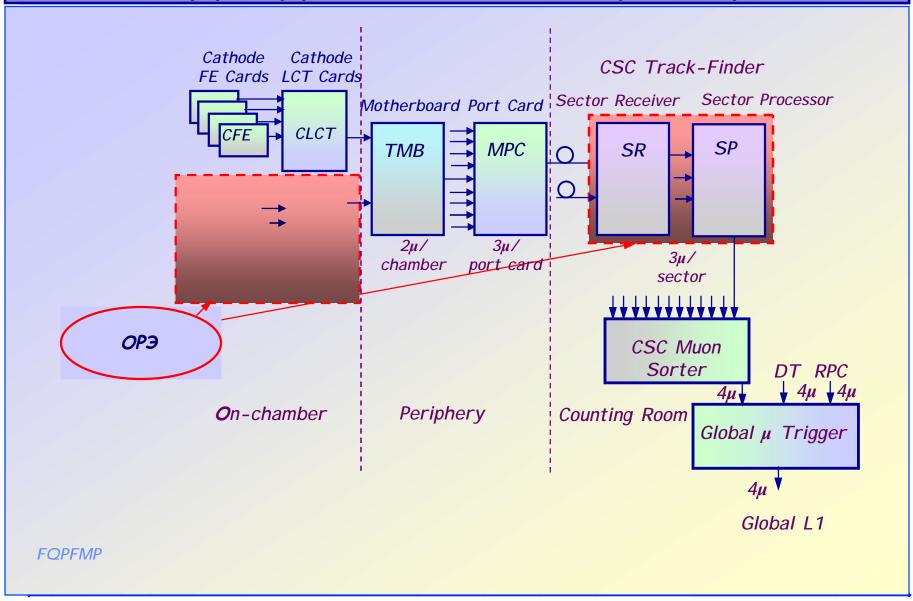

# Структура мюонного триггера

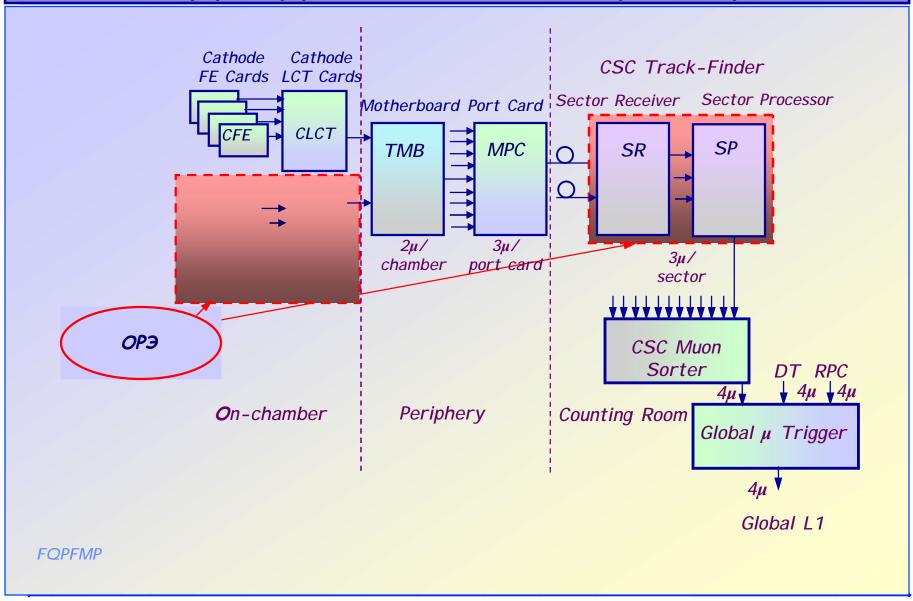

# CSC Придетекторная Электроника

AFE - карты

ALCT - модули

Каждая Катодная Стриповая

Камера посылает

примитивные треки на

Trigger Motherboard (TMB),

которые располагаютя в

периферийных крейтах (РС)

ТМВ- модули

Bcero 60 PCs на всю Endcap Muon System

**FQPFMP**

# CSC PC-TF Электроника

МРС-модуль

Данные от всех РС затем посылаются на один крейт Track Finder (TF) по оптическим кабелям

12 SP- модулей

**FQPFMP**

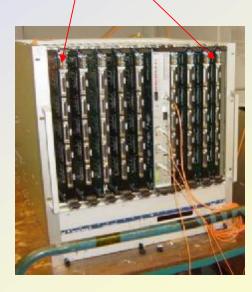

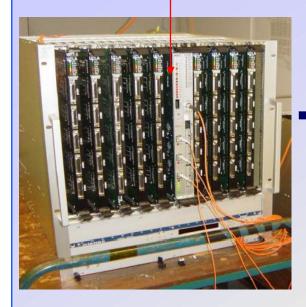

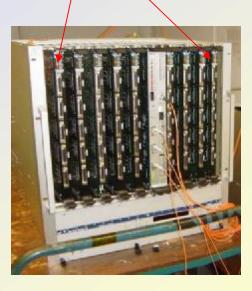

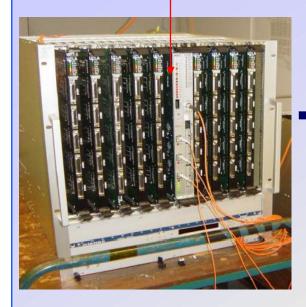

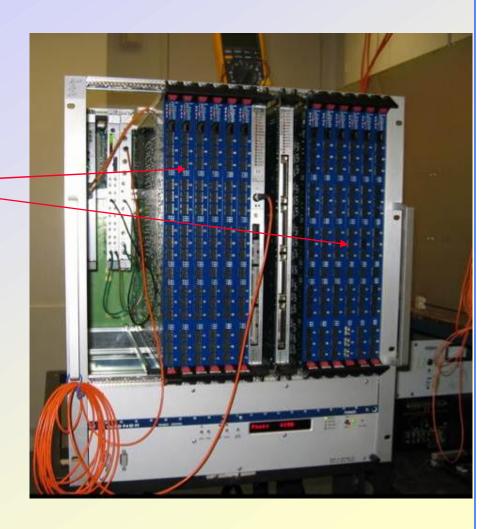

# CSC TF Kpent

Wiener 6023 crate with power supply,

VME64x J1 backplane and 4-fan tray unit

12 Sector Processors SP05 (UF/PNPI) †

Muon Sorter MS 2005 (Rice)

Clock and Control Board CCB2004 (Rice)

Custom 6U backplane rev. 2 (UF)

VME Crate Controller (SBS620 or CAEN 2718)

TTCvi and TTCvx (optional)

**ИТОГ** 2005 **ГОДА**

FOPFMP

# ТЕ Статус. Декабрь 2005

#### SP05 Модуль (CMS необходимо 12)

- **è Массовое производство завершено в Сентябре** 2005

- р 16/21 прошли все необходимые тесты

- р 5 имеют незначительные проблемы, будут решены Уваровым в UF

#### Мезонинная Карта (CMS: 12+1)

- **è** Массовое производство завершено в Сентябре 2005

- р 19/25 прошли все тесты

- р 5 имели к.з., возвращены вендору

#### QPLL дочерняя плата (CMS: 12)

- **è** Производство завершено (22)

- р Все QPLL проблемы решены

#### Новая ТF Специальная Плата Соединений 6U (CMS: 1)

- è Получены все детали (2 полностью собраны,

- 3 будут собраны)

#### DT-CSC Переходная Плата (CMS 12)

- è Произведено 17 (1 Ноября 2005)

- р Проходят тетирование в UF

- р Начало Февраля 2006 тестирование в ЦЕРНе (Уваров, Головцов?)

#### DDU адаптер ... для совместимости EMU DDU с ТF-крейтом

è разрабатывается

**FQPFMP**

# CSC/ DT Tестирование

#### CSC TF → DT TF Переходные Платы

- **è** 17 плат получены 1 Ноября 2005

- **è** Конструктивных проблем не обнаружено

- Одна плата прошла все тесты и отправлена в ЦЕРН. 16 плат должны быть экипированы лицевыми панелями и тестированы в ближайшее время

- è Плата прибыла в ЦЕРН и ожидает теста с электроникой DT Процессора

**FQPFMP**

### План 2006

- Завершение тестирования SP05s

- Завершение тестирования CSC-DT TBs

- DDU адаптер, отладки и тестироваие канала DDU DAQ

- Согласование планов в феврале в ЦЕРНе

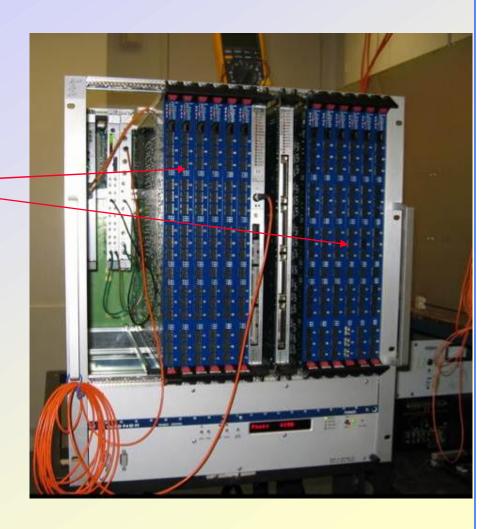

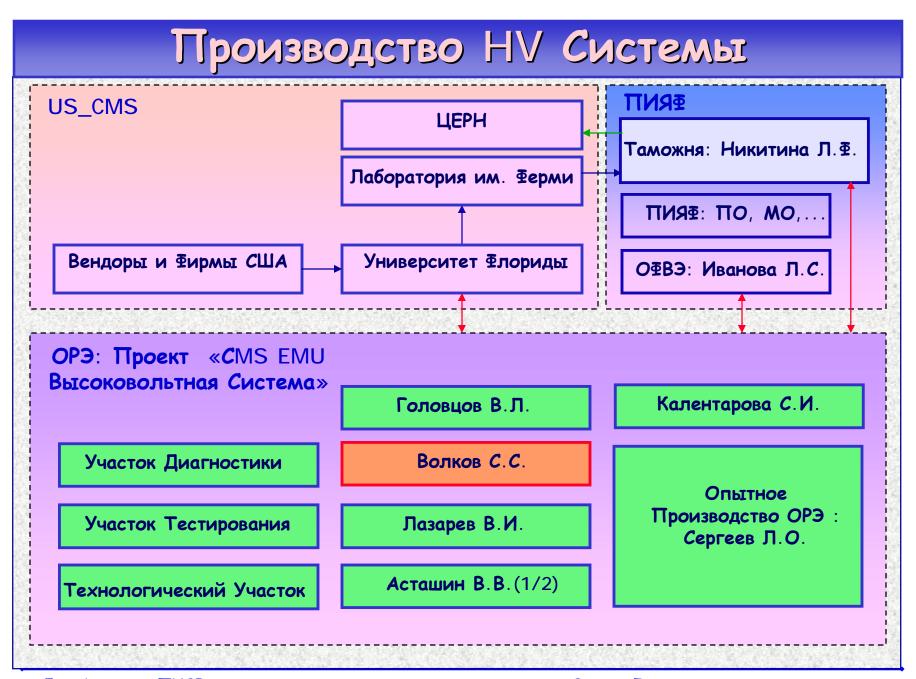

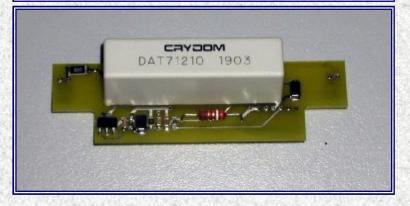

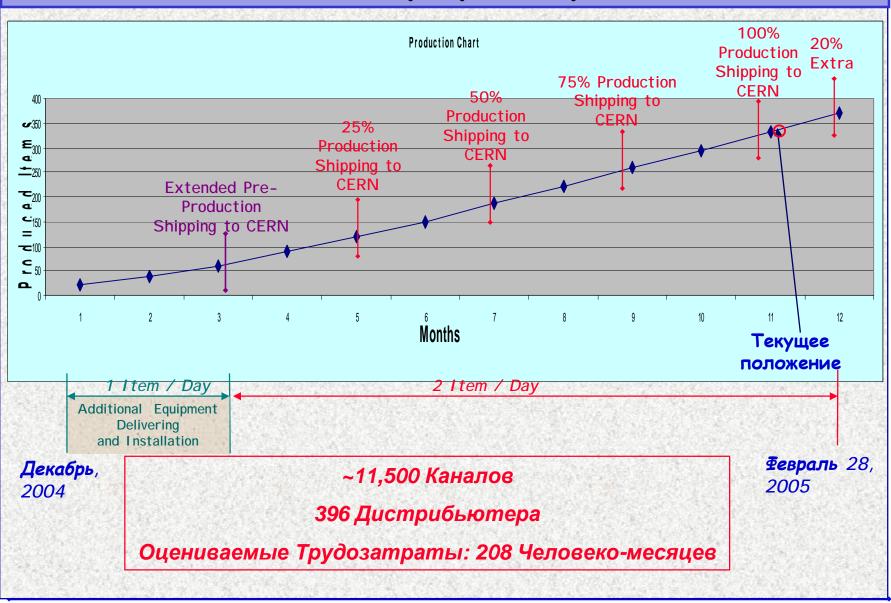

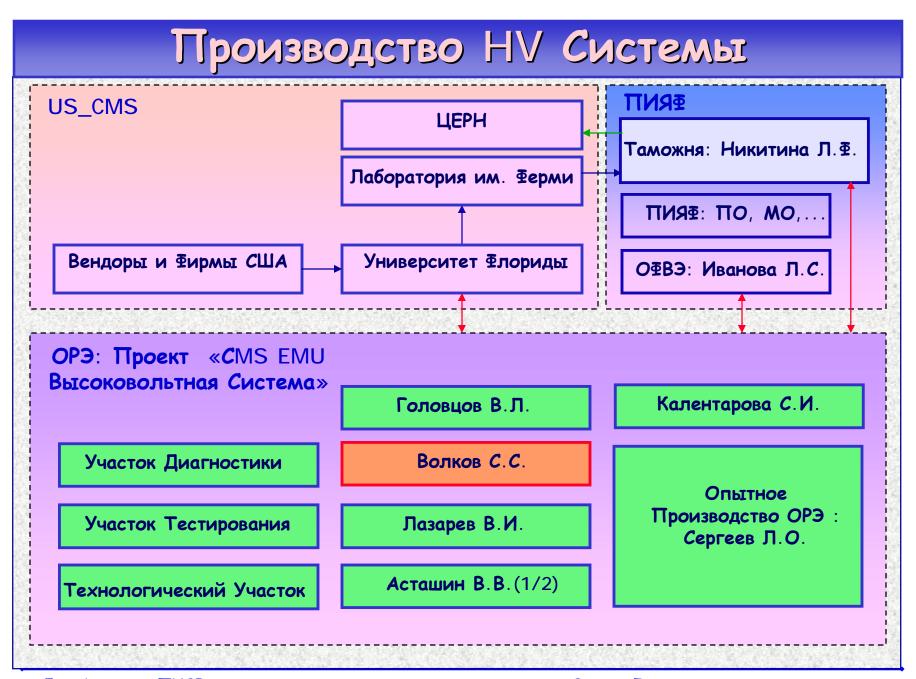

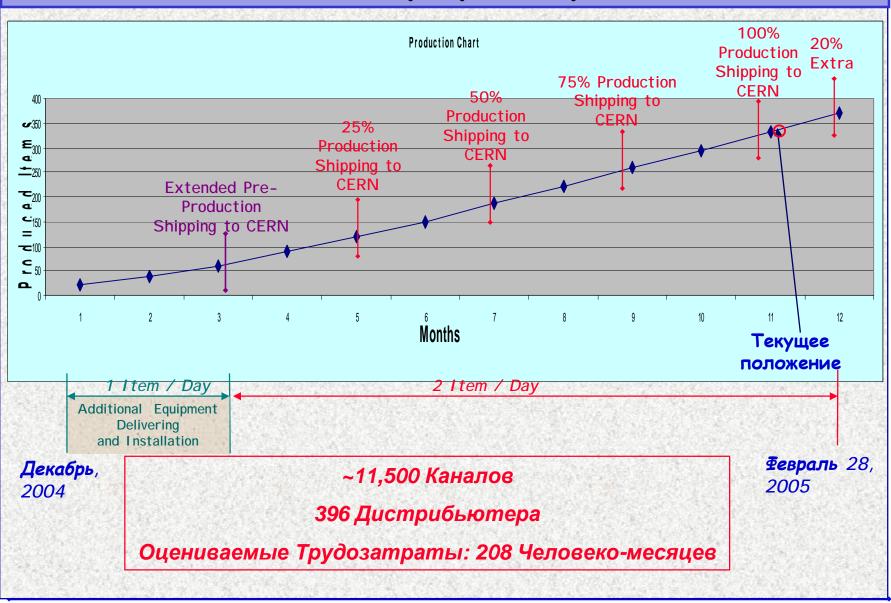

### CMS EMU Высоковольтная Система

Набор модулей HV системы Система предназначена для высоковольтного питания многосегментных проволочных камер Использует распределительные модули (дистрибьютеры), располагаемые рядом с детекторами При этом один высоковольтный источник питает

Система обеспечивает индивидуальное регулирование напряжения, мониторирование тока и напряжения в каждом сегменте

до 2000 сегментов

Дискретность измерения тока – ~20 nA Дискретность измерения и регулирования напряжения: ~ 2 V Диапазон регулирования напряжения – до 4 KV

Система разрабатывалась в коллаборации с Университетом Флориды (UF) с 2000

Тендер с фирмой CAEN на систему в 10000 каналов выигран в 2003 Стоимость проекта ~ 1.2 М\$

2005 - Массовое производство и монтаж системы на камерах в ЦЕРНе

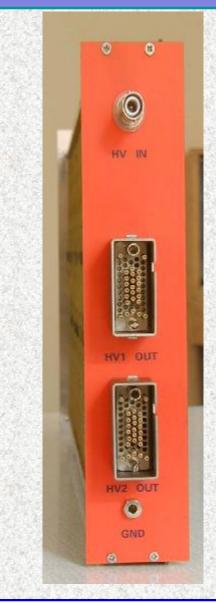

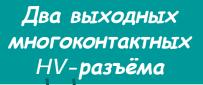

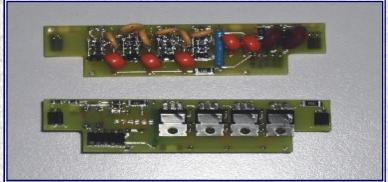

# EMU HV 36-Канальный Дистрибьютер

Два выходных многоконтактных HV-разъёма Разъём низковольтного питания

Входной HV- разъём 36 плат одноканальных регуляторов-сенсоров

Разъём магистрали управления и считывания

Модуль размером 40 х 230 х 540 мм (евромеханика)

# Передняя и задняя панели Дистрибьютера

# EMU HV Интерфейсная Карта Разъём РСІмагистрали FPGA Xilinx Разъём Магистрали Spartan II Управления/ Считывания

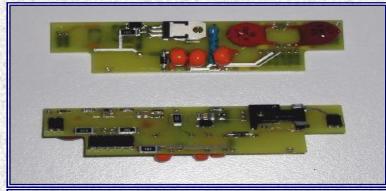

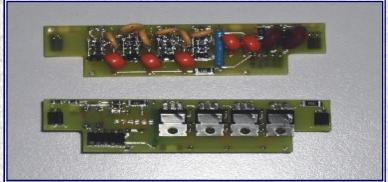

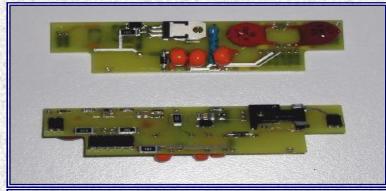

# EMU HV Сенсорные Платы

Плата Регулятора 1 КВ

Плата Регулятора 4 КВ

Плата Реле

### CMS EMU HV Выпускаемая Продукция

| Изделия                                   | Основное<br>Производство<br>(MOU 2003-3) | Дополнительное<br>Производство<br>(MOU2005-2) | Всего |

|-------------------------------------------|------------------------------------------|-----------------------------------------------|-------|

| 1KV regulator boards (RB1)                | 10072                                    | 1722                                          | 11794 |

| 4KV regulator boards (RB4)                | 690                                      | 125                                           | 815   |

| Relay boards (RB)                         | 690                                      | 125                                           | 815   |

| Distribution boards - 30 channels (DB-30) | 159                                      | 26                                            | 185   |

| Distribution boards - 36 channels (DB-36) | 129                                      | 22                                            | 151   |

| Master boards (MB)                        | 46                                       | 14                                            | 60    |

| Host Cards (HC)                           | 20                                       | -                                             | 20    |

Платы для ручного монтажа: 1KV, 4KV, RB - Всего 13424

Модули для ручной сборки и тестирования: DB-30, DB-36, MB - Всего 396

### CMS EMU HV Trah 2006

Март 2006 – Завершение Производства,

Отправка Груза в ЦЕРН

Консервация Части Производственного

и Тестового Оборудования

Переход на Производство HV системы для LHCb.

Предшествовавшие события:

Октябрь 2005 – выигрыш тендера у CAEN на производство 2000-канальной системы для LHCb и продолжение тендера на 600 каналов.

Последующие события пока на достигли подписания Договора

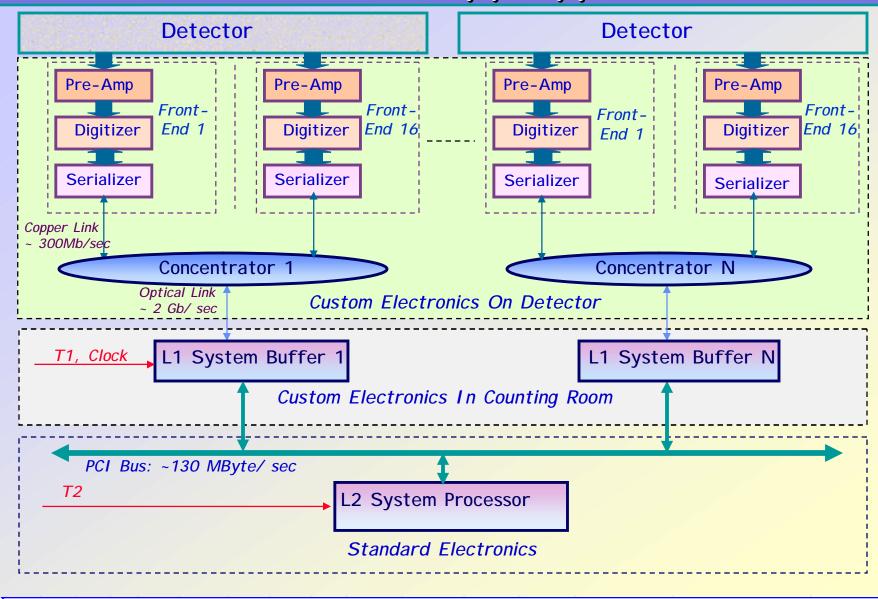

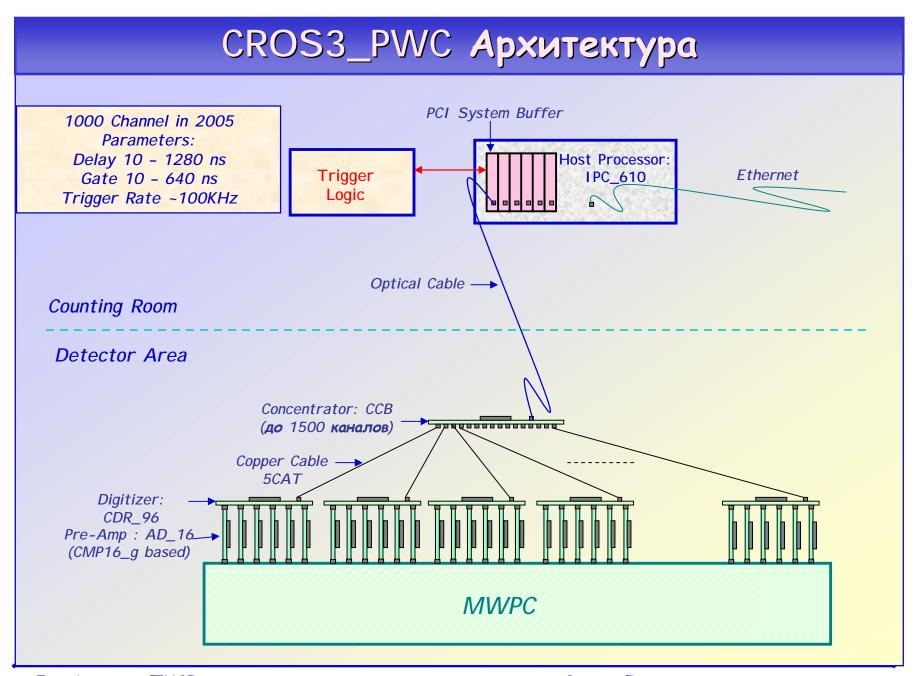

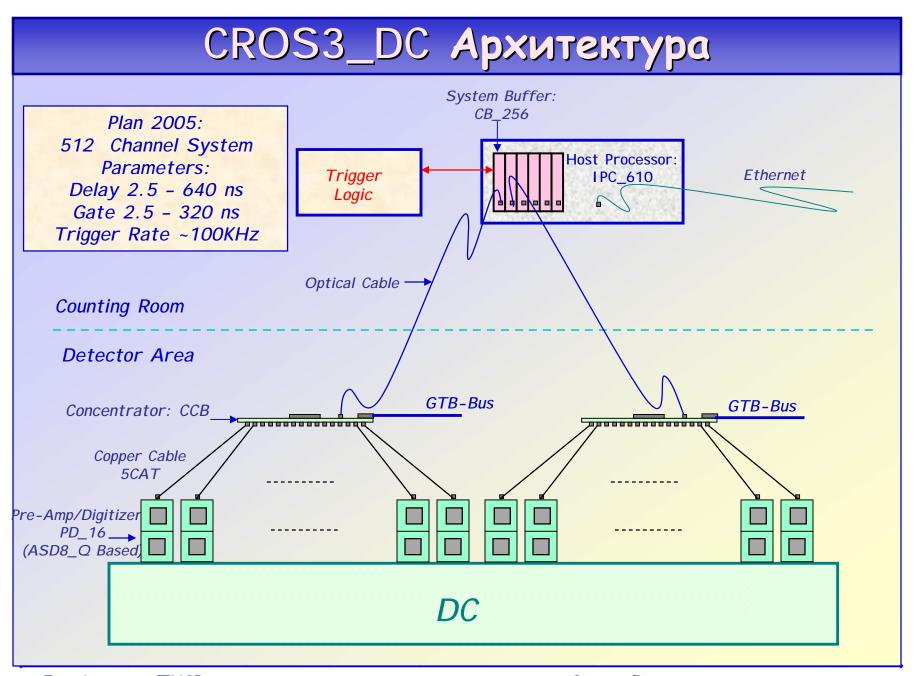

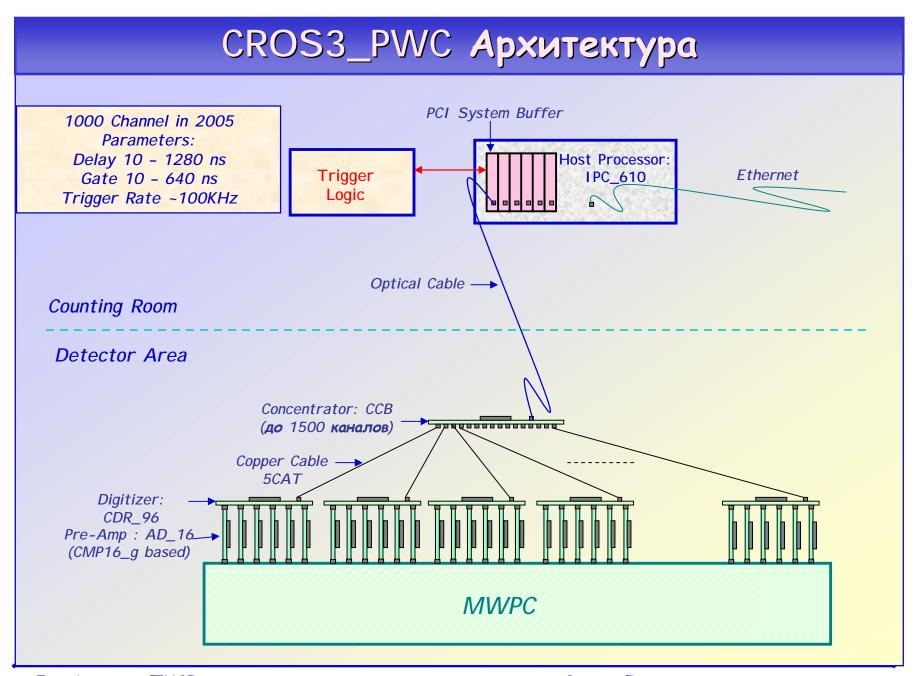

### CROS3 Система Считывания

CROS3 **Детекторная Сборка на** 96 **каналов**

CROS3 – координатная система считывания, разрабатываемая в ОРЭ с 2003.

- \* Учитывает достоинства (и недостатки) предыдущих систем CROS, CROS2.

- \* Использует достижения современных технологий, в том числе ASIC CMP16\_G, ASD-Q, FPGA Xilinx Spartan III и т.д.

- \* Адаптируется под конструкцию детектора. \* Позволяет организовать структуру "Data Push" – последовательной фильтрации данных.

#### Особенности Системы:

- \* Предусилитель, дискриминатор, задержка и считывание расположены непосредственно на детекторе

- \* Быстрое кодирование и считывание данных со скоростью >100 Mb/c по кабелям CAT5, CAT6 и до 2 Gb/c по оптическим кабелям

- \* Возможность измерения временного распределения срабатывания каналов в интервале «ворот» схемы совпадений с дискретностью до 2.5 ns

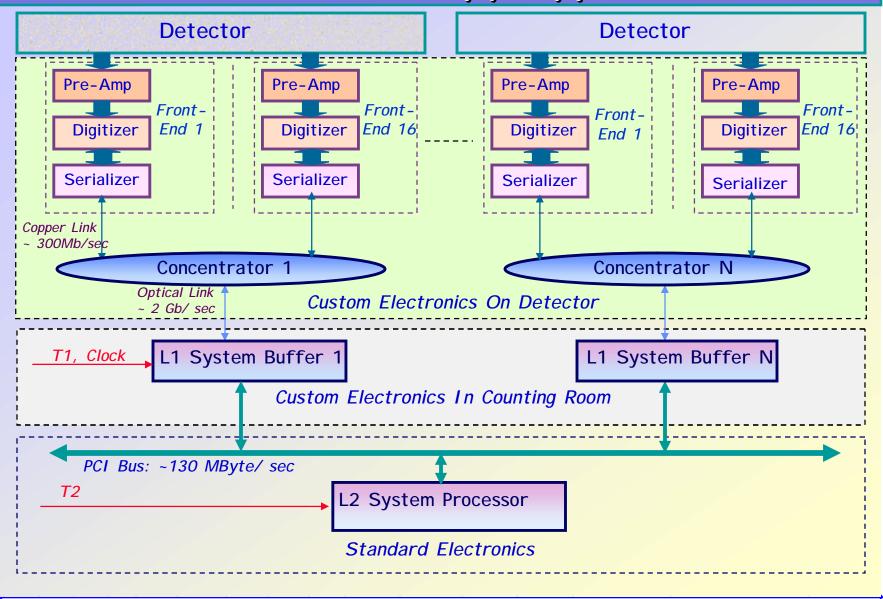

# CROS3 Структура

# CROS3\_PWC Изделия

# CROS3\_PWC Сборки

Системная детекторная плата CDR\_96 с нстановленными платами AD\_16

Системный концентратор ССВ\_16 и системная детекторная плата CDR\_96 с с кабелем 5САТ

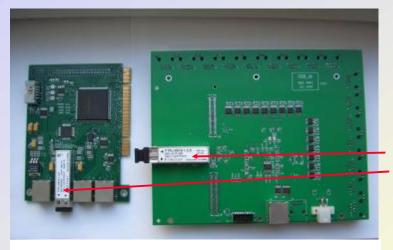

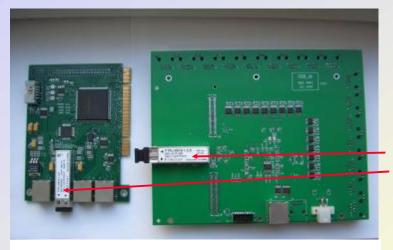

Системный концентратор ССВ\_16 и системный интерфейс SB\_16 с установленными оптическими приёмопередатчиками

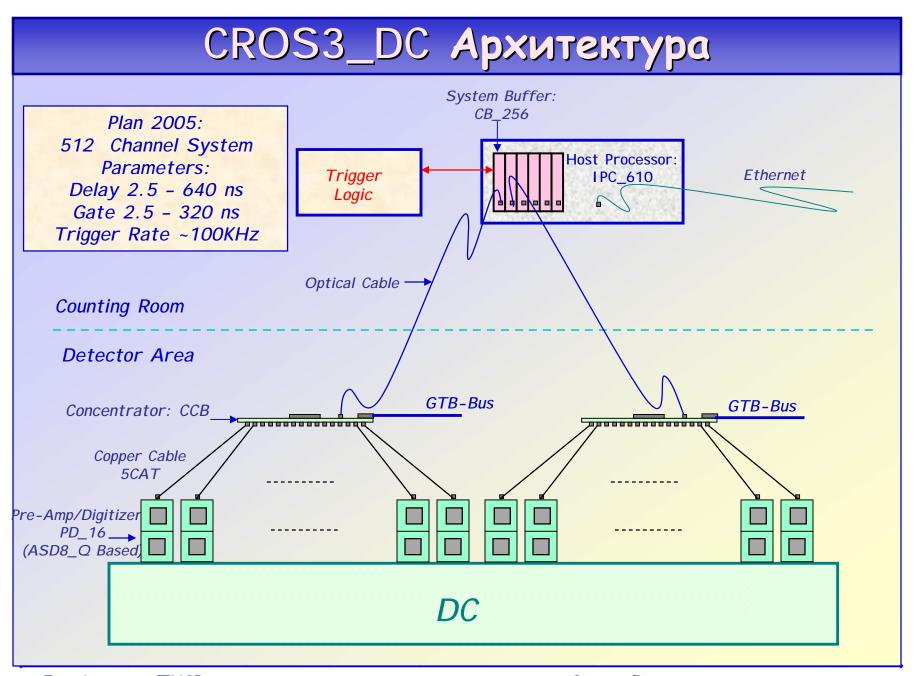

### CROS3\_DC Изделия

установленным адаптером GTB-

интерфейса

### CROS3\_PWC Текущий Статус

- 1. AD-16: в наличии 200 плат, спаяно 100 (1600 каналов).

- 2. CDR\_96: в наличии 4 платы (~400 каналов), спаяна 1. В середине января дозаявка оставшихся 30 плат.

- 3. ССВ\_16 в наличии 4, спаяны 3 (2 на 3000 каналов + запас).

- 4. SB\_16 в наличии 4 платы, спаяна 1. Остальные в процессе пайки.

- 5. Firmware в работе для CDR\_96, CCB\_16, SB\_16.

- 6. Test Software в работе для отладки и тестирования плат.

- 7. DAQ Software (Windows) в работе.

<u>Проблемы</u>: 1. Несколько позиций компонентов – резисторы и конденсаторы + оптический кабель.

2. Напряжённый график.

# CROS3\_DC Текущий Статус

- 1. DC-FE16: в наличии 40 плат (512 каналов + запас).

- 2. ССВ\_16: в наличии 4 платы, спаяна 1. Остальные в процессе пайки.

- 3. SB\_16 в наличии 4 платы, в процессе пайки.

- 4. Firmware в работе для DC\_FE16, CCB\_16, SB\_16.

- 5. Test Software в работе, готовность по мере постпления плат.

<u>Проблемы</u>: 1. Некоторые технические решаемые проблемы DC-FE16. Требуют квалифицированного (авторского) экспертного надзора.

2. Напряжённый график.

### CROS3 План 2006

- 1. Завершение настройки, тестирования и ввод в эксплуатацию 3000 каналов CROS3\_PWC.

- 2. Завершение настройки и тестирования 512-каналов CROS3\_DC.

### Инициативные работы

- 1. Развитие HV системы (группа С. Волкова)

- выпущена 32-канальная система с регулированием по каждому каналу в диапазоне 0-3000B;

- разработан прототип радиационно стойкого регулятора на 3 кВ, проводены испытания 16 регуляторов;

- осваивается выпуск всей номенклатуры изделий системы, как вариант для производства LHCb HV.

- 2. Развитие интерфейсов

- разработка USB-интерфейса для системы мониторирования пучка (Ю. Гавриков);

- адаптирование USB-интерфейса для HV-системы в 2006

# EMU CMS Alignment System

Система предназначена для контроля и мониторирования положения детекторов экспериментальной установки CMS. Использует оптические позиционные сенсоры, мониторирующие положение прямой линии лазера

Считывание данных сенсоров контролируется DSPпроцессорами. Система считывания (DCOPS) транслирует затем данные в Host DAQ

Разработка системы производится в коллаборации с Fermilab

# EMU CMS Alignment System 2005

Coctaв системы: Front-End Sensor Boards - 1216

DCOPS Readout Boards - 306

DCOPS Interface Boards - 62

Analog Interfaces - 56

Proximity Interface - 14

Temperature Conversion - 13

2005 : - Завершение интегрирования оборудования

- Завершение разработки системы распределения LV-питания

- Сборка электроники и механических частей

- Полный тест субсистем в VW8 (Fermilab)

- Развитие программного обеспечения

- Отправка оборудования в ЦЕРН

- Сборка оборудования на детекторе в ЦЕРНе

- Тест субсистем на детекторе

# Развитие инфраструктуры ОРЭ -2005

- Отремонтировано и оборудовано 80 м² рабочей площади

- Оборудовано 2 рабочих места инженеров-разработчиков

- Оборудовано 2 тестовых стенда настройки модулей

### Заключение

#### РОССИЙСКАЯ АКАДЕМИЯ НАУК ПЕТЕРБУРГСКИЙ ИНСТИТУТ ЯДЕРНОЙ ФИЗИКИ им. Б.П. КОНСТАНТИНОВА

#### ГОЛОВЦОВ Виктор Леонтьевич

Специализированные устройства первичной обработки информации в экспериментах по рассеянию частиц высоких энергий на малые углы

01.04.01 - приборы и методы экспериментальной физики

Диссертация на соискание учёной степени кандидата физико-математических наук

ЗАЩИТА СОСТОИТСЯ 26 ЯНВАРЯ 2006 г.

# С Новым 2006 годом!

# Отдел Радиоэлектроники 2005/ 2006 Отчёт и Планы

Головцов В.Л. Гатчина, Декабрь 2005

# OP3 2005

| Всего Сотрудников   | 30 |

|---------------------|----|

| Научных Сотрудников | 9  |

| Инженеров           | 12 |

| Техников            | 9  |

| Женщин              | 11 |

| Мужчин              | 19 |

| Пенсионеров         | 19 |

| В возрасте до 40    | 5  |

| Средний возраст     | 50 |

| Уволилось в 2005    | 2  |

### Основные Тематические Группы 2005

### Track Finder (CMS):

Головцов В.Л., Уваров Л.Н.

**FOPFMP**

#### CROS3:

Головцов В.Л., Бондарь Н.Ф., Яцюра В.И., Голяш А.Г., Лобачёв Е.А.

### CMS EMU HV (CMS)

Волков С.С., Лазарев В.И., Исаев Н.Б., Бондарев С.В., Сергеев Л.О. Мыльникова А.В., Гулина Н.М.

### Alignment (CMS):

Скнарь В. А.

### **CMS Track Finder**

Серийные модули Процесора (SP05)

Track Finder разработан для мюонной триггерной системы CMS.

Реализуется как 12 Процессоров, каждый из которых идентифицирует до 3 лучших мюонных треков в 60-градусном азимутальном секторе. Анализирует входные примитивные треки (сегменты) от индивидуальных камер, восстанавливает полные треки по четырём камерам, измеряет поперечный импульс Pt

Ноябрь 1998 - подписание MOU с UF. 1999 - начало проектирования

2000-2001- выпуск первогоПрототипа, отладка и тестирование

В 2001 г. предложено новое идеологическое решение, позволившее реализовать второй прототип Процессора на одной сверхбольшой микросхеме FPGA.

В результате время решения Процессора сократилось с 375 ns до 175 ns, а число плат Track Finder - с 48 до 12 (один 9U-крейт VME)

2002-2003 - выпуск Прототипа SP02, отладка и тестирование

2004 - выпуск Прототипа SP04, отладка и тестирование

2005 - выпуск сигнального образца и массовое производство SP05

FOPFMP

## Потоки данных мюонного триггера

# Структура мюонного триггера

# CSC Придетекторная Электроника

AFE - карты

ALCT - модули

Каждая Катодная Стриповая Камера посылает примитивные треки на Trigger Motherboard (TMB), которые располагаютя в периферийных крейтах (PC) ТМВ- модули

Bceго 60 PCs на всю Endcap Muon System

**FQPFMP**

# CSC PC-TF Электроника

МРС-модуль

Данные от всех РС затем посылаются на один крейт Track Finder (TF) по оптическим кабелям

12 SP- модулей

**FQPFMP**

# CSC TF Kpent

Wiener 6023 crate with power supply,

VME64x J1 backplane and 4-fan tray unit

12 Sector Processors SP05 (UF/PNPI) †

Muon Sorter MS 2005 (Rice)

Clock and Control Board CCB2004 (Rice)

Custom 6U backplane rev.2 (UF)

VME Crate Controller (SBS620 or CAEN 2718)

TTCvi and TTCvx (optional)

**ИТОГ** 2005 **ГОДА**

FOPFMP

# ТЕ Статус. Декабрь 2005

#### SP05 Модуль (CMS необходимо 12)

- **è Массовое производство завершено в Сентябре** 2005

- р 16/21 прошли все необходимые тесты

- р 5 имеют незначительные проблемы, будут решены Уваровым в UF

#### Мезонинная Карта (CMS: 12+1)

- **è** Массовое производство завершено в Сентябре 2005

- р 19/25 прошли все тесты

- р 5 имели к.з., возвращены вендору

#### QPLL дочерняя плата (CMS: 12)

- **è** Производство завершено (22)

- р Все QPLL проблемы решены

#### Новая ТF Специальная Плата Соединений 6U (CMS: 1)

- è Получены все детали (2 полностью собраны,

- 3 будут собраны)

#### DT-CSC Переходная Плата (CMS 12)

- è Произведено 17 (1 Ноября 2005)

- р Проходят тетирование в UF

- р Начало Февраля 2006 тестирование в ЦЕРНе (Уваров, Головцов?)

### DDU адаптер ... для совместимости EMU DDU с ТF-крейтом

è разрабатывается

**FQPFMP**

# CSC/ DT Tестирование

### CSC TF → DT TF Переходные Платы

- **è** 17 плат получены 1 Ноября 2005

- **è** Конструктивных проблем не обнаружено

- Одна плата прошла все тесты и отправлена в ЦЕРН. 16 плат должны быть экипированы лицевыми панелями и тестированы в ближайшее время

- è Плата прибыла в ЦЕРН и ожидает теста с электроникой DT Процессора

**FQPFMP**

### План 2006

- Завершение тестирования SP05s

- Завершение тестирования CSC-DT TBs

- DDU адаптер, отладки и тестироваие канала DDU DAQ

- Согласование планов в феврале в ЦЕРНе

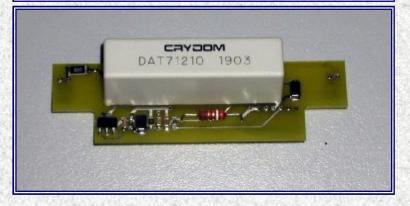

### CMS EMU Высоковольтная Система

Набор модулей HV системы Система предназначена для высоковольтного питания многосегментных проволочных камер Использует распределительные модули (дистрибьютеры), располагаемые рядом с детекторами При этом один высоковольтный источник питает до 2000 сегментов

Система обеспечивает индивидуальное регулирование напряжения, мониторирование тока и напряжения в каждом сегменте

Дискретность измерения тока – ~20 nA Дискретность измерения и регулирования напряжения: ~ 2 V Диапазон регулирования напряжения – до 4 KV

Система разрабатывалась в коллаборации с Университетом Флориды (UF) с 2000

Тендер с фирмой CAEN на систему в 10000 каналов выигран в 2003 Стоимость проекта ~ 1.2 М\$

2005 - Массовое производство и монтаж системы на камерах в ЦЕРНе

# EMU HV 36-Канальный Дистрибьютер

Разъём низковольтного питания

Входной HV- разъём 36 плат одноканальных регуляторов-сенсоров

Разъём магистрали управления и считывания

Модуль размером 40 х 230 х 540 мм (евромеханика)

# Передняя и задняя панели Дистрибьютера

# EMU HV Интерфейсная Карта Разъём РСІмагистрали FPGA Xilinx Разъём Магистрали Spartan II Управления/ Считывания

# EMU HV Сенсорные Платы

Плата Регулятора 1 КВ

Плата Регулятора 4 КВ

Плата Реле

### CMS EMU HV Выпускаемая Продукция

| Изделия                                   | Основное<br>Производство<br>(MOU 2003-3) | Дополнительное<br>Производство<br>(MOU2005-2) | Всего |

|-------------------------------------------|------------------------------------------|-----------------------------------------------|-------|

| 1KV regulator boards (RB1)                | 10072                                    | 1722                                          | 11794 |

| 4KV regulator boards (RB4)                | 690                                      | 125                                           | 815   |

| Relay boards (RB)                         | 690                                      | 125                                           | 815   |

| Distribution boards - 30 channels (DB-30) | 159                                      | 26                                            | 185   |

| Distribution boards - 36 channels (DB-36) | 129                                      | 22                                            | 151   |

| Master boards (MB)                        | 46                                       | 14                                            | 60    |

| Host Cards (HC)                           | 20                                       | -                                             | 20    |

Платы для ручного монтажа: 1KV, 4KV, RB - Всего 13424

Модули для ручной сборки и тестирования: DB-30, DB-36, MB - Всего 396

### CMS EMU HV Trah 2006

Март 2006 – Завершение Производства,

Отправка Груза в ЦЕРН

Консервация Части Производственного

и Тестового Оборудования

Переход на Производство HV системы для LHCb.

Предшествовавшие события:

Октябрь 2005 – выигрыш тендера у CAEN на производство 2000-канальной системы для LHCb и продолжение тендера на 600 каналов.

Последующие события пока на достигли подписания Договора

### CROS3 Система Считывания

CROS3 **Детекторная Сборка на** 96 **каналов**

CROS3 – координатная система считывания, разрабатываемая в ОРЭ с 2003.

- \* Учитывает достоинства (и недостатки) предыдущих систем CROS, CROS2.

- \* Использует достижения современных технологий, в том числе ASIC CMP16\_G, ASD-Q, FPGA Xilinx Spartan III и т.д.

- \* Адаптируется под конструкцию детектора. \* Позволяет организовать структуру "Data Push" – последовательной фильтрации данных.

#### Особенности Системы:

- \* Предусилитель, дискриминатор, задержка и считывание расположены непосредственно на детекторе

- \* Быстрое кодирование и считывание данных со скоростью >100 Mb/c по кабелям CAT5, CAT6 и до 2 Gb/c по оптическим кабелям

- \* Возможность измерения временного распределения срабатывания каналов в интервале «ворот» схемы совпадений с дискретностью до 2.5 ns

# CROS3 Структура

# CROS3\_PWC Изделия

# CROS3\_PWC Сборки

Системная детекторная плата CDR\_96 с нстановленными платами AD\_16

Системный концентратор ССВ\_16 и системная детекторная плата CDR\_96 с с кабелем 5САТ

Системный концентратор ССВ\_16 и системный интерфейс SB\_16 с установленными оптическими приёмопередатчиками

### CROS3\_DC Изделия

установленным адаптером GTB-

интерфейса

## CROS3\_PWC Текущий Статус

- 1. AD-16: в наличии 200 плат, спаяно 100 (1600 каналов).

- 2. CDR\_96: в наличии 4 платы (~400 каналов), спаяна 1. В середине января дозаявка оставшихся 30 плат.

- 3. ССВ\_16 в наличии 4, спаяны 3 (2 на 3000 каналов + запас).

- 4. SB\_16 в наличии 4 платы, спаяна 1. Остальные в процессе пайки.

- 5. Firmware в работе для CDR\_96, CCB\_16, SB\_16.

- 6. Test Software в работе для отладки и тестирования плат.

- 7. DAQ Software (Windows) в работе.

<u>Проблемы</u>: 1. Несколько позиций компонентов – резисторы и конденсаторы + оптический кабель.

2. Напряжённый график.

# CROS3\_DC Текущий Статус

- 1. DC-FE16: в наличии 40 плат (512 каналов + запас).

- 2. ССВ\_16: в наличии 4 платы, спаяна 1. Остальные в процессе пайки.

- 3. SB\_16 в наличии 4 платы, в процессе пайки.

- 4. Firmware в работе для DC\_FE16, CCB\_16, SB\_16.

- 5. Test Software в работе, готовность по мере постпления плат.

<u>Проблемы</u>: 1. Некоторые технические решаемые проблемы DC-FE16. Требуют квалифицированного (авторского) экспертного надзора.

2. Напряжённый график.

### CROS3 План 2006

- 1. Завершение настройки, тестирования и ввод в эксплуатацию 3000 каналов CROS3\_PWC.

- 2. Завершение настройки и тестирования 512-каналов CROS3\_DC.

### Инициативные работы

- 1. Развитие HV системы (группа С. Волкова)

- выпущена 32-канальная система с регулированием по каждому каналу в диапазоне 0-3000B;

- разработан прототип радиационно стойкого регулятора на 3 кВ, проводены испытания 16 регуляторов;

- осваивается выпуск всей номенклатуры изделий системы, как вариант для производства LHCb HV.

- 2. Развитие интерфейсов

- разработка USB-интерфейса для системы мониторирования пучка (Ю. Гавриков);

- адаптирование USB-интерфейса для HV-системы в 2006

## EMU CMS Alignment System

Система предназначена для контроля и мониторирования положения детекторов экспериментальной установки CMS. Использует оптические позиционные сенсоры, мониторирующие положение прямой линии лазера

Считывание данных сенсоров контролируется DSPпроцессорами. Система считывания (DCOPS) транслирует затем данные в Host DAQ

Разработка системы производится в коллаборации с Fermilab

# EMU CMS Alignment System 2005

Состав системы: Front-End Sensor Boards - 1216

DCOPS Readout Boards - 306

DCOPS Interface Boards - 62

Analog Interfaces - 56

Proximity Interface - 14

Temperature Conversion - 13

2005 : - Завершение интегрирования оборудования

- Завершение разработки системы распределения LV-питания

- Сборка электроники и механических частей

- Полный тест субсистем в VW8 (Fermilab)

- Развитие программного обеспечения

- Отправка оборудования в ЦЕРН

- Сборка оборудования на детекторе в ЦЕРНе

- Тест субсистем на детекторе

# Развитие инфраструктуры ОРЭ -2005

- Отремонтировано и оборудовано 80 м2 рабочей площади

- Оборудовано 2 рабочих места инженеров-разработчиков

- Оборудовано 2 тестовых стенда настройки модулей

### Заключение

#### РОССИЙСКАЯ АКАДЕМИЯ НАУК ПЕТЕРБУРГСКИЙ ИНСТИТУТ ЯДЕРНОЙ ФИЗИКИ им. Б.П. КОНСТАНТИНОВА

#### ГОЛОВЦОВ Виктор Леонтьевич

Специализированные устройства первичной обработки информации в экспериментах по рассеянию частиц высоких энергий на малые углы

01.04.01 - приборы и методы экспериментальной физики

Диссертация на соискание учёной степени кандидата физико-математических наук

ЗАЩИТА СОСТОИТСЯ 26 ЯНВАРЯ 2006 г.

# С Новым 2006 годом!